Flip Flop Circuits (OCR A Level Computer Science): Revision Note

Exam code: H446

D Type Flip Flops

What is a D type flip flop?

In A Level Computer Science, a D type flip flop is a fundamental component in digital circuits and computer memory

Can be referred to as Positive Edge Triggered

Key features

Contains two stable states, making it a type of bistable circuit

Used to store the state of 1 bit of data

Changes state on the edge of the clock pulse

Components

Data input (D)

Clock input (CLK)

Two outputs: Q and NOT(Q)

D Type Flip Flip Components

Operation

On the rising edge of the clock pulse:

If D is high (1), Q goes high and NOT(Q) goes low

If D is low (0), Q goes low and NOT(Q) goes high

The state of Q holds or "remembers" its value until the next rising clock edge

Use cases

Forms the basis of most types of flip flops and latches

Used in shift registers, counters, and memory units

Helpful in edge-triggered devices, synchronous circuits, and data storage

Examiner Tips and Tricks

You will not be asked to recall the logic gates that make up a D-type flip flop and they can be made from various different gates

They are often built using NAND gates which are AND gates that have their output inverted:

D Type Flip Flip Logic Gates

Worked Example

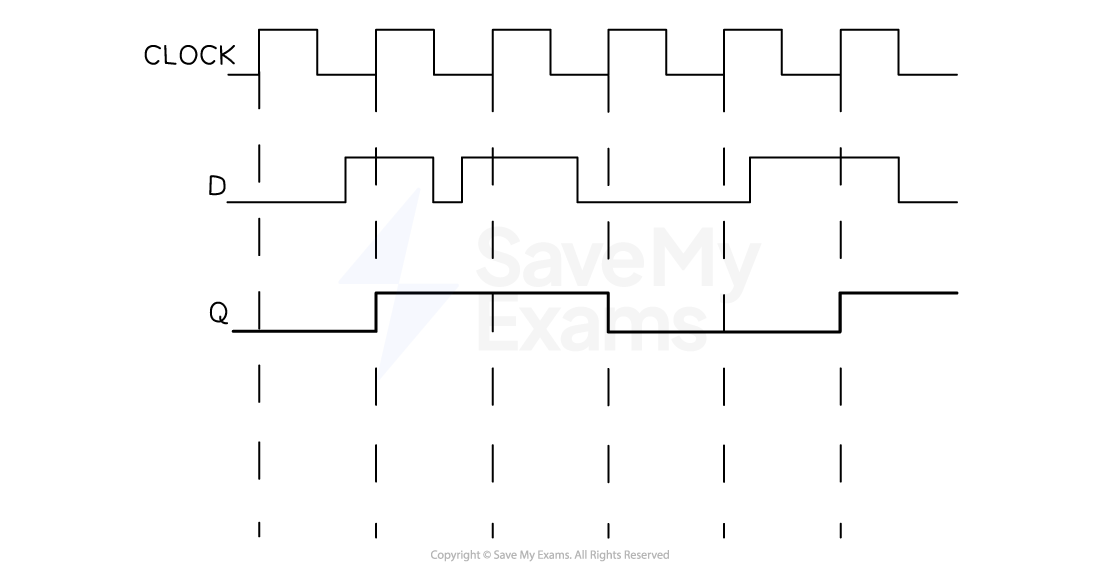

Draw the output of the Flip Flop on the diagram below

D Type Flip Flop Question

For a question like this remember that the output line Q that you are asked to draw wants to be the same as the input D BUT it can only change when the clock signal changes from low to high (i.e. at the dotted lines)

At the start assume Q starts the same as D (low in this case)

Then draw it along from left to right until you get to a vertical dotted line (in an exam you would draw these lines on to help you if they weren’t there

At each dotted line, Q has the chance to change to whatever D is

D Type Flip Flop Working 1

So at the first line, D is low so Q stays low

At the second dotted line D has changed to high so now Q can become high

D Type Flip Flop Working 2

Q now stays high until the next rising edge of the clock (the next dotted line) where it gets another chance to change, but here D is still high so Q stays high

D Type Flip Flop Working 3

And you continue to do this until you reach the right hand side of the diagram

D Type Flip Flop Working 4

Unlock more, it's free!

Did this page help you?